参考資料

**MAX3232** JAJSJJ9O - JANUARY 2000 - REVISED JUNE 2021

# MAX3232 3V~5.5V、マルチチャネル RS-232 ライン・ドライバおよびレシー バ、 ±15kV ESD 保護

## 1 特長

- 人体モデル (HBM) で ±15kV を超える RS-232 バス・ピン ESD 保護

- TIA/EIA-232-F および ITU V.28 規格の要件に適合

- 3V~5.5V の V<sub>CC</sub> 電源で動作

- 最大 250kbit/s で動作

- 2 つのドライバと 2 つのレシーバ

- 低消費電流:標準値 300µA

- 外付けコンデンサ:4×0.1µF

- 3.3V 電源で 5V ロジック入力を受容

- 代替の高速ピン互換デバイス (1Mbit/s)

- SN65C3232 (-40°C∼85°C)

- SN75C3232 (0°C∼70°C)

## 2 アプリケーション

- 産業用 PC

- 有線ネットワーク

- データ・センターおよびエンタープライズ・ネットワーク

- バッテリ駆動システム

- PDA

- ノートブック PC

- ノート PC

- パームトップ PC

- ハンドヘルド機器

### 3 概要

MAX3232 は 2 つのライン・ドライバ、2 つのライン・レシー バ、1 つのデュアル・チャージ・ポンプ回路で構成されて おり、±15kV のピン間 (シリアル・ポート接続ピン、GND を 含む) ESD 保護機能を備えています。このデバイスは、 TIA/EIA-232-F のスペックを満たし、非同期通信コントロ ーラとシリアルポート・コネクタの間の電気的インターフェイ スとして機能します。チャージ・ポンプと 4 つの小さな外付 けコンデンサにより、3V~5.5Vの単一電源で動作できま す。本デバイスは最大 250kbit/s のデータ信号速度、最 大 30V/µs のドライバ出力スルーレートで動作します。

#### 製品情報

| 部品番号    | パッケージ <sup>(1)</sup> | 本体サイズ            |

|---------|----------------------|------------------|

|         | SOIC (D) (16)        | 9.90mm × 3.91mm  |

| MAY222  | SSOP (DB) (16)       | 6.20mm × 5.30mm  |

| MAX3232 | SOIC (DW) (16)       | 10.30mm × 7.50mm |

|         | TSSOP (PW) (16)      | 5.00mm × 4.40mm  |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

# 目次

| 1 特長                                                        |                | 8.2 機能ブロック図                                                                                                                                    |            |

|-------------------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 2 アプリケーション                                                  |                | 8.3 機能説明                                                                                                                                       |            |

| 3 概要                                                        |                | 8.4 デバイスの機能モード                                                                                                                                 |            |

| 4 改訂履歴                                                      |                | 9 アプリケーションと実装                                                                                                                                  |            |

| 5 ピン構成および機能                                                 |                | 9.1 アプリケーション情報                                                                                                                                 |            |

| 6 仕様                                                        |                | 9.2 標準的なアプリケーション                                                                                                                               |            |

| 6.1 絶対最大定格                                                  |                | 10 電源に関する推奨事項                                                                                                                                  |            |

| 6.2 ESD 定格                                                  |                | 11 レイアウト                                                                                                                                       |            |

| 6.3 推奨動作条件                                                  |                | 11.1 レイアウトのガイドライン                                                                                                                              |            |

| 6.4 熱に関する情報                                                 |                | 11.2 レイアウト例                                                                                                                                    |            |

| 6.5 電気的特性 — デバイス                                            |                | 12 デバイスおよびドキュメントのサポート                                                                                                                          |            |

| 6.6 電気的特性 — ドライバ                                            |                | 12.1 Receiving Notification of Documentation Up                                                                                                |            |

| 6.7 電気的特性 — レシーバ                                            |                | 12.2 Support Resources                                                                                                                         |            |

| 6.8 スイッチング特性                                                |                | 12.3 商標                                                                                                                                        |            |

| 6.9 代表的特性                                                   | <mark>7</mark> | 12.4 静電気放電に関する注意事項                                                                                                                             |            |

| 7 パラメータ測定情報                                                 |                | 12.5 Glossary                                                                                                                                  |            |

| 8 詳細説明                                                      | 9              | 13 メカニカル、パッケージ、および注文情報                                                                                                                         | 14         |

| 8.1 概要                                                      | 9              |                                                                                                                                                |            |

|                                                             | 有線ネッ           | (June 2021)<br>トワーク、データ・センターおよびエンタープライズ・コ                                                                                                      |            |

|                                                             |                | īを変更                                                                                                                                           |            |

| Changes from Revision M (April 2017) to Revi                | ision N        | (June 2017)                                                                                                                                    | Page       |

| ・ 「パッケージ情報」表を変更                                             |                |                                                                                                                                                |            |

| Changes from Revision L (March 2017) to Rev                 | vision l       | M (April 2017)                                                                                                                                 | Page       |

| <ul><li>次のように変更:表 9-1 の V<sub>CC</sub> 列で「±」を「~」に</li></ul> | 二変更            |                                                                                                                                                | 12         |

| Changes from Revision K (January 2015) to R                 | Revisio        | n L (March 2017)                                                                                                                               | Page       |

| • 図 9-1 のピン 16 (V <sub>CC</sub> ) を変更                       |                |                                                                                                                                                | 11         |

| Changes from Revision J (January 2014) to R                 | Revisio        | า K (January 2015)                                                                                                                             | Page       |

| セクション、「機能説明」セクション、「デバイスの核<br>関する推奨事項」セクション、「レイアウト」セクショ      | 幾能モー<br>ン、「デ   | E」表、「 <i>ESD 定格</i> 」表、「 <i>熱に関する情報</i> 」表、「 <i>代表</i><br>-ド」セクション、「 <i>アプリケーションと実装</i> 」セクション、<br><i>バイスおよびドキュメントのサポート</i> 」セクション、「 <i>メカ</i> | 「電源にカニカノル、 |

| Changes from Revision I (January 2004) to Re                | evision        | J (January 2014)                                                                                                                               | Page       |

| • 新しい TI データシート・フォーマットにドキュメント                               | トを更新           | - 仕様変更なし                                                                                                                                       | 1          |

「*注文情報*」表を削除.......1

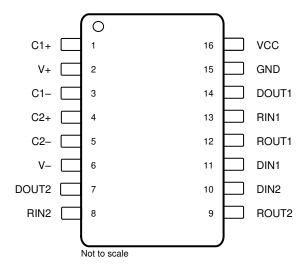

## 5 ピン構成および機能

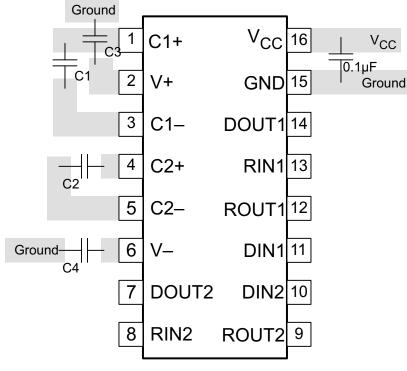

図 5-1. D、DB、DW、または PW パッケージ、16 ピン SOIC、 SSOP、または TSSOP の上面図

表 5-1. ピン機能

| ピン              |    | ALC: NOT | 3V 111                                   |

|-----------------|----|----------|------------------------------------------|

| 名称              | 番号 | 種類       | l in |

| C1+             | 1  | _        | C1 コンデンサの正のリード                           |

| V+              | 2  | 0        | チャージ・ポンプの正の出力 (ストレージ・コンデンサのみ)            |

| C1-             | 3  | _        | C1 コンデンサの負のリード                           |

| C2+             | 4  | _        | C2 コンデンサの正のリード                           |

| C2-             | 5  | _        | C2 コンデンサの負のリード                           |

| V-              | 6  | 0        | チャージ・ポンプの負の出力 (ストレージ・コンデンサのみ)            |

| DOUT2           | 7  | 0        | RS232 ライン・データ出力 (リモート RS232 システムへ)       |

| DOUT1           | 14 | 0        | RS232 ライン・データ出力 (リモート RS232 システムへ)       |

| RIN2            | 8  | I        | RS232 ライン・データ入力 (リモート RS232 システムから)      |

| RIN1            | 13 | I        | RS232 ライン・データ入力 (リモート RS232 システムから)      |

| ROUT2           | 9  | 0        | ロジック・データ出力 (UART 〜)                      |

| ROUT1           | 12 | 0        | ロジック・データ出力 (UART 〜)                      |

| DIN2            | 10 | I        | ロジック・データ入力 (UART から)                     |

| DIN1            | 11 | I        | ロジック・データ入力 (UART から)                     |

| GND             | 15 | _        | グランド                                     |

| V <sub>CC</sub> | 16 | _        | 電源電圧、外部の 3V~5.5V 電源に接続                   |

### 6 仕様

### 6.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) (1)

|                  |                           |      |      | 最小値            | 最大値  | 単位 |

|------------------|---------------------------|------|------|----------------|------|----|

| V <sub>CC</sub>  | 電源電圧の範囲 <sup>(2)</sup>    |      |      | -0.3           | 6    | V  |

| V+               | 正の出力電源電圧範囲 <sup>(2)</sup> |      |      | -0.3           | 7    | V  |

| V-               | 負の出力電源電圧範囲 <sup>(2)</sup> |      |      | -7             | 0.3  | V  |

| V+ – V–          | 電源電圧の差異 <sup>(2)</sup>    |      |      |                | 13   | V  |

| VI               | 入力電圧範囲                    | ドライバ |      | -0.3           | 6    | V  |

| ١٧١              | 八刀竜圧靶囲                    | レシーバ |      | -25            | 25   | V  |

| Vo               | 出力電圧範囲                    | ドライバ |      | -13.2          | 13.2 | V  |

| <b>V</b> O       | 口力電圧範囲レシーバ                |      | -0.3 | $V_{CC} + 0.3$ | V    |    |

| T <sub>J</sub>   | 動作時の仮想接合部温度               |      |      |                | 150  | °C |

| T <sub>stg</sub> | 保管温度範囲                    |      |      | -65            | 150  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) すべての電圧はネットワーク GND を基準にしています。

### 6.2 ESD 定格

|                            |       |                                                                           | 値     | 単位 |

|----------------------------|-------|---------------------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> 静電気放電   |       | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、<br>RIN、DOUT、GND ピン <sup>(1)</sup> | 15000 |    |

|                            | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、<br>すべてのピン <sup>(1)</sup>          | 3000  | V  |

| デバイスネ<br>ピン <sup>(2)</sup> |       | デバイス帯電モデル (CDM)、JEDEC 規格 JESD22-C101 準拠、 すべての ピン <sup>(2)</sup>           | 1000  |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスで安全な製造が可能であると記載されています。

## 6.3 推奨動作条件

(図 9-1 を参照)(1)

|                 |                        |        |                        | 最小値 | 公称值 | 最大値 | 単位 |

|-----------------|------------------------|--------|------------------------|-----|-----|-----|----|

| V <sub>CC</sub> | 電源電圧                   |        | V <sub>CC</sub> = 3.3V | 3   | 3.3 | 3.6 | V  |

| V CC            | 电你电灯                   | 电/尿电/上 |                        |     | 5   | 5.5 | V  |

| V <sub>IH</sub> | ドライバの High レベル入力電圧 DIN | DIN    | V <sub>CC</sub> = 3.3V | 2   |     |     | V  |

|                 |                        | DIN    | V <sub>CC</sub> = 5V   | 2.4 |     |     | V  |

| V <sub>IL</sub> | ドライバの Low レベル入力電圧      | DIN    |                        |     |     | 0.8 | V  |

| \/              | ドライバの入力電圧              | DIN    |                        | 0   |     | 5.5 | V  |

| VI              | レシーバの入力電圧              | RIN    |                        | -25 |     | 25  | V  |

| T <sub>A</sub>  |                        |        |                        | 0   |     | 70  | °C |

|                 | 自由気流での動作温度             |        | MAX3232I               | -40 |     | 85  |    |

(1) テスト条件は、 $V_{CC} = 3.3V \pm 0.3V$  では  $C1 \sim C4 = 0.1 \mu F$ 、 $V_{CC} = 5V \pm 0.5V$  では  $C1 = 0.047 \mu F$ 、 $C2 \sim C4 = 0.33 \mu F$  です。

#### 6.4 熱に関する情報

|                       |                      |          | MAX3232   |           |            |      |  |

|-----------------------|----------------------|----------|-----------|-----------|------------|------|--|

|                       | 熱評価基準 <sup>(1)</sup> | SOIC (D) | SSOP (DB) | SOIC (DW) | TSSOP (PW) | 単位   |  |

|                       |                      |          | 16 Ľ      | シ         |            |      |  |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗         | 85.9     | 103.1     | 66.6      | 108.2      | °C/W |  |

| R <sub>0JC(top)</sub> | 接合部からケース (上面) への熱抵抗  | 43.1     | 49.2      | 32.4      | 39.0       | °C/W |  |

| $R_{\theta JB}$       | 接合部から基板への熱抵抗         | 44.5     | 54.8      | 31.9      | 54.4       | °C/W |  |

| ΨЈТ                   | 接合部から上面への熱特性パラメータ    | 10.1     | 12        | 8.4       | 3.3        | °C/W |  |

| ΨЈВ                   | 接合部から基板への熱特性パラメータ    | 44.1     | 54.1      | 31.5      | 53.8       | °C/W |  |

| R <sub>0JC(bot)</sub> | 接合部からケース (底面) への熱抵抗  | n/a      | n/a       | n/a       | n/a        | °C/W |  |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

### 6.5 電気的特性 — デバイス

電源電圧の推奨範囲と動作温度範囲内 (特に記述のない限り)(2) (図 9-1 を参照)

|                 | パラメータ |      | テスト条件                        | 最小値 標準値 (1) | 最大値 | 単位 |

|-----------------|-------|------|------------------------------|-------------|-----|----|

| I <sub>CC</sub> | 電源電流  | 無負荷、 | $V_{CC}$ = 3.3 $V\sim$ 5 $V$ | 0.3         | 1   | mA |

- (1) すべての標準値は、 $V_{CC}$  = 3.3V または  $V_{CC}$  = 5V、 $T_A$  = 25 $^{\circ}$ Cでの値です。

- (2) テスト条件は、 $V_{CC}$  = 3.3V ± 0.3V では C1 $\sim$  C4 = 0.1 $\mu$ F、 $V_{CC}$  = 5V ± 0.5V では C1 = 0.047 $\mu$ F、C2 $\sim$  C4 = 0.33 $\mu$ F です。

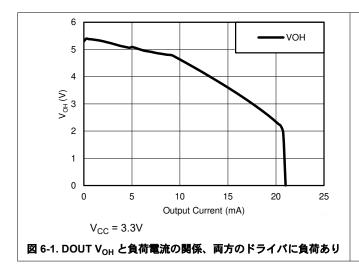

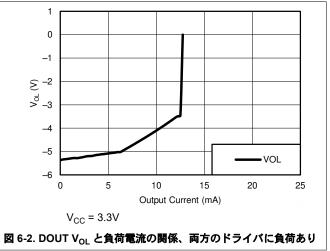

### 6.6 電気的特性 — ドライバ

電源電圧の推奨範囲と動作温度範囲内 (特に記述のない限り)(3) (図 9-1 を参照)

|                     | パラメータ        | テスト条件                                                                       |                                       | 最小値 | 標 <b>準値</b> | 最大値 | 単位   |

|---------------------|--------------|-----------------------------------------------------------------------------|---------------------------------------|-----|-------------|-----|------|

| V <sub>OH</sub>     | High レベル出力電圧 | D <sub>OUT</sub> $\varepsilon$ GND $\sim \mathcal{O}$ R <sub>L</sub> = 3kΩ、 | D <sub>IN</sub> = GND で測定             | 5   | 5.4         |     | V    |

| V <sub>OL</sub>     | Low レベル出力電圧  | $D_{OUT} \stackrel{\sim}{\sim} GND \stackrel{\sim}{\sim} R_L = 3k\Omega$    | D <sub>IN</sub> = V <sub>CC</sub> で測定 | -5  | -5.4        |     | V    |

| I <sub>IH</sub>     | High レベル入力電流 | V <sub>I</sub> = V <sub>CC</sub>                                            |                                       |     | ±0.01       | ±1  | μΑ   |

| I <sub>IL</sub>     | Low レベル入力電流  | V <sub>I</sub> はGND                                                         |                                       |     | ±0.01       | ±1  | μΑ   |

| I <sub>OS</sub> (2) | 短絡出力電流       | V <sub>CC</sub> = 3.6V                                                      | V <sub>O</sub> = 0V                   |     | ±35         | ±60 | mA   |

| 'os '               |              | V <sub>CC</sub> = 5.5V                                                      | V <sub>O</sub> = 0V                   |     | ±33         | 100 | IIIA |

| r <sub>O</sub>      | 出力抵抗         | V <sub>CC</sub> , V+' N- = 0N                                               | V <sub>O</sub> = ±2V                  | 300 | 10M         |     | Ω    |

- (1) すべての標準値は、V<sub>CC</sub> = 3.3V または V<sub>CC</sub> = 5V、T<sub>A</sub> = 25℃での値です。

- (2) 短絡時間は、デバイスの絶対消費電力定格を超えないように制御する必要があります。また、一度に複数の出力を短絡させないでください。

- (3) テスト条件は、 $V_{CC}$  = 3.3V ± 0.3V では C1 $\sim$ C4 = 0.1 $\mu$ F、 $V_{CC}$  = 5V ± 0.5V では C1 = 0.047 $\mu$ F、C2 $\sim$ C4 = 0.33 $\mu$ F です。

## 6.7 電気的特性 — レシーバ

電源電圧の推奨範囲と動作温度範囲内 (特に記述のない限り)(2) (図 9-1 を参照)

|                   | パラメータ                                           | テスト条件                     | 最小値                   | 標準値 <sup>(1)</sup>    | 最大値 | 単位 |

|-------------------|-------------------------------------------------|---------------------------|-----------------------|-----------------------|-----|----|

| V <sub>OH</sub>   | High レベル出力電圧                                    | I <sub>OH</sub> = -1mA    | V <sub>CC</sub> - 0.6 | V <sub>CC</sub> - 0.1 |     | V  |

| V <sub>OL</sub>   | Low レベル出力電圧                                     | I <sub>OL</sub> = 1.6mA   |                       |                       | 0.4 | V  |

| V <sub>IT+</sub>  | 立ち上がり入力スレッショルド電圧                                | V <sub>CC</sub> = 3.3V    |                       | 1.5                   | 2.4 | V  |

| VIT+              |                                                 | V <sub>CC</sub> = 5V      |                       | 1.8                   | 2.4 | v  |

| V <sub>IT</sub> _ | 立ち下がり入力スレッショルド電圧                                | V <sub>CC</sub> = 3.3V    | 0.6                   | 1.2                   |     | V  |

| VIT-              |                                                 | V <sub>CC</sub> = 5V      | 0.8                   | 1.5                   |     | v  |

| $V_{\text{hys}}$  | 入力ヒステリシス (V <sub>IT+</sub> – V <sub>IT-</sub> ) |                           |                       | 0.3                   |     | V  |

| r <sub>l</sub>    | 入力抵抗                                            | V <sub>I</sub> = ±3V∼±25V | 3                     | 5                     | 7   | kΩ |

- (1) すべての標準値は、V<sub>CC</sub> = 3.3V または V<sub>CC</sub> = 5V、T<sub>A</sub> = 25℃での値です。

- (2) テスト条件は、 $V_{CC}$  = 3.3V ± 0.3V では C1 $\sim$ C4 = 0.1 $\mu$ F、 $V_{CC}$  = 5V ± 0.5V では C1 = 0.047 $\mu$ F、C2 $\sim$ C4 = 0.33 $\mu$ F です。

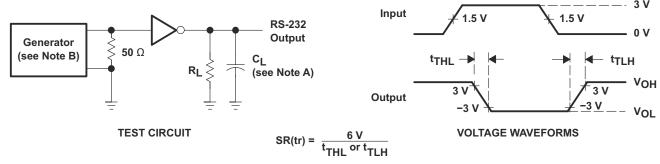

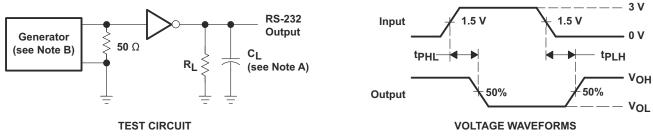

## 6.8 スイッチング特性

電源電圧の推奨範囲と動作温度範囲内 (特に記述のない限り)(3) (図 9-1 を参照)

|                    | パラメータ                                                   | ペラメータ テスト条件                                 |                             | 最小値 | 標準値 (1) | 最大値 | 単位     |

|--------------------|---------------------------------------------------------|---------------------------------------------|-----------------------------|-----|---------|-----|--------|

|                    |                                                         | $R_L = 3k\Omega$                            | C <sub>L</sub> = 1000pF     |     |         |     |        |

|                    | 最大データ・レート                                               | <b>1</b> つの <b>D</b> <sub>OUT</sub> スイッチング、 | 図 7-1 を参照                   | 150 | 250     |     | kbit/s |

| <b>t</b>           | t <sub>sk(n)</sub> ドライバのパルス・スキュー(2) R <sub>I</sub> = 3I |                                             | C <sub>L</sub> = 150∼2500pF |     | 300     |     | ns     |

| t <sub>sk(p)</sub> | [P/1/10) (P/1/14 17)                                    | $R_L = 3k\Omega \sim 7k\Omega$              | 図 7-2 を参照                   |     | 300     |     | 113    |

| SR(tr)             | スルーレート、遷移領域                                             | $R_L = 3k\Omega \sim 7k\Omega$              | C <sub>L</sub> = 150~1000pF | 6   |         | 30  | V/µs   |

| SIX(II)            | (図 7-1 を参照)                                             | V <sub>CC</sub> = 5V                        | C <sub>L</sub> = 150~2500pF | 4   |         | 30  | V/μS   |

| t <sub>PLH®)</sub> | 伝搬遅延時間、Low レベルから High レベル出力まで                           | -C <sub>I</sub> = 150pF                     |                             |     | 300     |     |        |

| t <sub>PHL®)</sub> | 伝搬遅延時間、High レベルから Low レベル出力まで                           | - 130рі                                     |                             |     | 300     |     | ns     |

| t <sub>sk(p)</sub> | レシーバのパルス・スキュー(3)                                        |                                             |                             |     | 300     |     |        |

- (1) すべての標準値は、 $V_{CC}$  = 3.3V または  $V_{CC}$  = 5V、 $T_A$  = 25 $^{\circ}$ Cでの値です。

- (2) パルス・スキューは、同じデバイスの各チャネルの |tplh tphl| と定義されます。

- (3) テスト条件は、 $V_{CC}$  = 3.3V ± 0.3V では C1~C4 = 0.1 $\mu$ F、 $V_{CC}$  = 5V ± 0.5V では C1 = 0.047 $\mu$ F、C2~C4 = 0.33 $\mu$ F です。

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 6.9 代表的特性

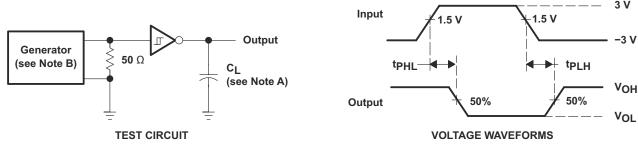

## 7パラメータ測定情報

- A. CL にはプローブと治具の容量が含まれます。

- B. パルス・ジェネレータの特性は、以下のとおりです。 PRR = 250kbit/s、  $Z_0$  = 50 $\Omega$ 、デューティ・サイクル 50%、  $t_f \le$  10ns、  $t_f \le$  10ns

#### 図 7-1. ドライバのスルーレート

- A. CLにはプローブと治具の容量が含まれます。

- B. パルス・ジェネレータの特性は、以下のとおりです。 PRR = 250kbit/s、  $Z_0$  = 50 $\Omega$ 、デューティ・サイクル 50%、  $t_r \le$  10ns、  $t_f \le$  10ns

#### 図 7-2. ドライバのパルス・スキュー

- A. C<sub>I</sub>にはプローブと治具の容量が含まれます。

- B. パルス・ジェネレータの特性は、以下のとおりです。  $Z_0$  =  $50\Omega$ 、デューティ・サイクル 50%、 $t_r \le 10$ ns、 $t_f \le 10$ ns

図 7-3. レシーバの伝搬遅延時間

### 8 詳細説明

#### 8.1 概要

MAX3232 は 2 つのライン・ドライバ、2 つのライン・レシーバ、1 つのデュアル・チャージ・ポンプ回路で構成されており、±15kV のピン間 (シリアル・ポート接続ピン、GND を含む) ESD 保護機能を備えています。このデバイスは、TIA/ EIA-232-F の要件を満たし、非同期通信コントローラとシリアルポート・コネクタの間の電気的インターフェイスとして機能します。チャージ・ポンプと 4 つの小さな外付けコンデンサにより、3V~5.5V の単一電源で動作できます。本デバイスは最大 250kbit/s のデータ信号速度、最大 30V/μs のドライバ出力スルーレートで動作します。出力はグランドへの短絡から保護されています。

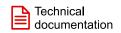

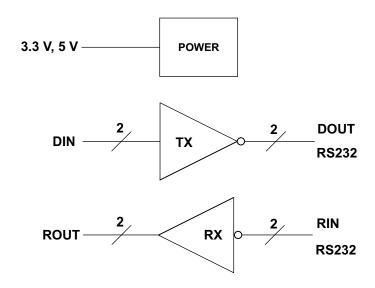

#### 8.2 機能ブロック図

### 8.3 機能説明

#### 8.3.1 電源

このパワー・ブロックは、4個の外付けコンデンサを必要とするチャージ・ポンプを使用して、V+ および V- ピンの電圧を上昇、反転、および調整します。

### 8.3.2 RS232 ドライバ

2 つのドライバは、標準ロジック・レベルを RS232 レベルにインターフェイスします。両方の DIN 入力は、有効な High または Low レベルである必要があります。

#### 8.3.3 RS232 レシーバ

2 つのレシーバは、RS232 レベルを標準ロジック・レベルにインターフェイスします。入力が開放されている場合、ROUT の出力は High になります。各 RIN 入力には、内部標準 RS232 負荷が含まれています。

## 8.4 デバイスの機能モード

表 8-1. 各ドライバ(1)

| INPUT<br>DIN | OUTPUT<br>DOUT |

|--------------|----------------|

| L            | Н              |

| Н            | L              |

(1) H = High レベル、L = Low レベル

表 8-2. 各レシーバ(1)

| INPUT<br>RIN | OUTPUT<br>ROUT |

|--------------|----------------|

| L            | Н              |

| Н            | L              |

| 開放           | н              |

(1) H = High レベル、L = Low レベル、開放 = 入力が切断されている、または接続されているドライバがオフ

## 8.4.1 V<sub>CC</sub> に 3V~5.5V の電源を供給

デバイスは通常動作になります。

## 8.4.2 V<sub>CC</sub> への電源供給なし (V<sub>CC</sub> = 0V)

MAX3232 に電源を供給しない場合、アクティブなリモート RS232 デバイスに安全に接続できます。

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 9アプリケーションと実装

#### 注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

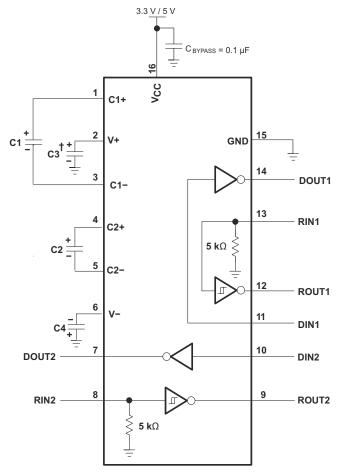

適切に動作させるには、図 9-1 に示すようにコンデンサを追加します。

## 9.2 標準的なアプリケーション

ROUT と DIN は、UART または汎用ロジック・ラインに接続します。 RIN と DOUT の各ラインは、RS232 コネクタまたはケーブルに接続します。

$\dagger$  C3 は  $V_{CC}$  または GND に接続できます。

- A. 表記の抵抗値は公称値です。

- B. 無極性セラミック・コンデンサも使用できます。極性化タンタル・コンデンサまたは電解コンデンサを使用する場合は、図のように接続する必要があります。

図 9-1. 代表的な動作回路とコンデンサの値

#### 9.2.1 設計要件

- 推奨される V<sub>CC</sub> は 3.3V または 5V です。3V~5.5V も可能です。

- 最大推奨ビット・レートは 250kbit/s です。

表 9-1. V<sub>CC</sub> とコンデンサの値

| V <sub>cc</sub> | V <sub>CC</sub> C1 |        |  |  |

|-----------------|--------------------|--------|--|--|

| 3.3V ± 0.3V     | 0.1µF              | 0.1µF  |  |  |

| 5V ± 0.5V       | 0.047µF            | 0.33µF |  |  |

| 3V∼5.5V         | 0.1µF              | 0.47µF |  |  |

### 9.2.2 詳細な設計手順

- すべての DIN、FORCEOFF、FORCEON 入力は、有効な Low または High ロジック・レベルに接続する必要があります。

- 最高の性能を得るため、VCC レベルに基づいてコンデンサの値を選択してください。

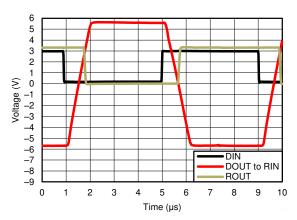

#### 9.2.3 アプリケーション曲線

$V_{CC} = 3.3V$

図 9-2, 250kbit/s ドライバからレシーバへのループバックのタイミング波形

## 10 電源に関する推奨事項

$V_{CC}$  は  $3V\sim5.5V$  の範囲である必要があります。チャージ・ポンプ・コンデンサは、図 9-1 の表を使用して選択する必要があります。

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

## 11 レイアウト

## 11.1 レイアウトのガイドライン

外付けコンデンサの配線は短くしてください。これは、立ち上がり時間と立ち下がり時間が最短の C1 および C2 ノードではより重要です。

## 11.2 レイアウト例

図 11-1. レイアウトの図

## 12 デバイスおよびドキュメントのサポート

## 12.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 12.2 Support Resources

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 12.3 商標

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

#### 12.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい ESD 対策をとらないと、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 12.5 Glossary

TI Glossary This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。このデータシートのブラウザ対応版については、左側にあるナビゲーションを参照してください。

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

21-Feb-2024 www.ti.com

#### **PACKAGING INFORMATION**

| Orderable Device | Status  | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | <b>Device Marking</b> (4/5) | Samples |

|------------------|---------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-----------------------------|---------|

| MAX3232CDBR      | ACTIVE  | SSOP         | DB                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | MA3232C                     | Samples |

| MAX3232CDR       | ACTIVE  | SOIC         | D                  | 16   | 2500           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | MAX3232C                    | Samples |

| MAX3232CDW       | LIFEBUY | SOIC         | DW                 | 16   | 40             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | MAX3232C                    |         |

| MAX3232CDWG4     | NRND    | SOIC         | DW                 | 16   | 40             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | MAX3232C                    |         |

| MAX3232CDWR      | LIFEBUY | SOIC         | DW                 | 16   | 2000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | 0 to 70      | MAX3232C                    |         |

| MAX3232CPWR      | ACTIVE  | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | MA3232C                     | Samples |

| MAX3232CPWRE4    | ACTIVE  | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | MA3232C                     | Samples |

| MAX3232CPWRG4    | ACTIVE  | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | MA3232C                     | Samples |

| MAX3232IDBR      | ACTIVE  | SSOP         | DB                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MB3232I                     | Samples |

| MAX3232IDBRE4    | ACTIVE  | SSOP         | DB                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MB3232I                     | Samples |

| MAX3232IDW       | LIFEBUY | SOIC         | DW                 | 16   | 40             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MAX3232I                    |         |

| MAX3232IDWR      | ACTIVE  | SOIC         | DW                 | 16   | 2000           | RoHS & Green | NIPDAU   SN                   | Level-1-260C-UNLIM | -40 to 85    | MAX3232I                    | Samples |

| MAX3232IDWRE4    | NRND    | SOIC         | DW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MAX3232I                    |         |

| MAX3232IDWRG4    | LIFEBUY | SOIC         | DW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MAX3232I                    |         |

| MAX3232IPWR      | ACTIVE  | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MB3232I                     | Samples |

| MAX3232IPWRE4    | ACTIVE  | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MB3232I                     | Samples |

| MAX3232IPWRG4    | ACTIVE  | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | MB3232I                     | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

## PACKAGE OPTION ADDENDUM

www.ti.com 21-Feb-2024

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF MAX3232:

Enhanced Product : MAX3232-EP

NOTE: Qualified Version Definitions:

• Enhanced Product - Supports Defense, Aerospace and Medical Applications

www.ti.com 11-Dec-2023

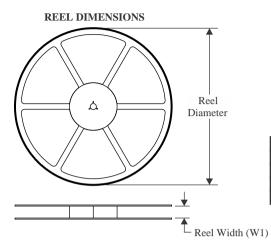

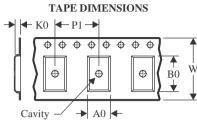

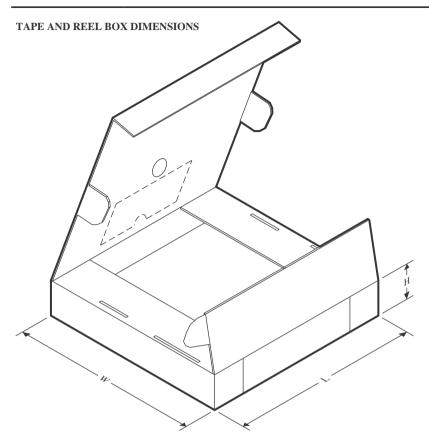

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

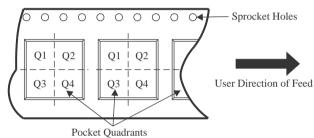

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| MAX3232CDBR   | SSOP            | DB                 | 16 | 2000 | 330.0                    | 16.4                     | 8.35       | 6.6        | 2.4        | 12.0       | 16.0      | Q1               |

| MAX3232CDR    | SOIC            | D                  | 16 | 2500 | 330.0                    | 16.4                     | 6.5        | 10.3       | 2.1        | 8.0        | 16.0      | Q1               |

| MAX3232CDWR   | SOIC            | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

| MAX3232CPWR   | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| MAX3232CPWR   | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| MAX3232CPWRG4 | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| MAX3232IDBR   | SSOP            | DB                 | 16 | 2000 | 330.0                    | 16.4                     | 8.35       | 6.6        | 2.4        | 12.0       | 16.0      | Q1               |

| MAX3232IDWR   | SOIC            | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

| MAX3232IDWRG4 | SOIC            | DW                 | 16 | 2000 | 330.0                    | 16.4                     | 10.75      | 10.7       | 2.7        | 12.0       | 16.0      | Q1               |

| MAX3232IPWR   | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| MAX3232IPWR   | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| MAX3232IPWRG4 | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| MAX3232IPWRG4 | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 11-Dec-2023

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| MAX3232CDBR   | SSOP         | DB              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232CDR    | SOIC         | D               | 16   | 2500 | 356.0       | 356.0      | 35.0        |

| MAX3232CDWR   | SOIC         | DW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| MAX3232CPWR   | TSSOP        | PW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232CPWR   | TSSOP        | PW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232CPWRG4 | TSSOP        | PW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232IDBR   | SSOP         | DB              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232IDWR   | SOIC         | DW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| MAX3232IDWRG4 | SOIC         | DW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| MAX3232IPWR   | TSSOP        | PW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232IPWR   | TSSOP        | PW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232IPWRG4 | TSSOP        | PW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

| MAX3232IPWRG4 | TSSOP        | PW              | 16   | 2000 | 356.0       | 356.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 11-Dec-2023

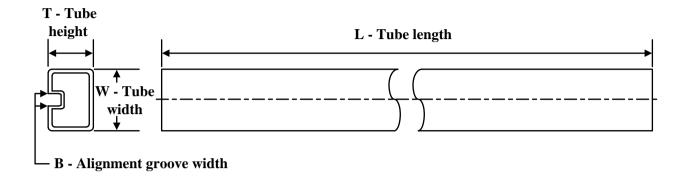

### **TUBE**

#### \*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| MAX3232CDW   | DW           | SOIC         | 16   | 40  | 506.98 | 12.7   | 4826   | 6.6    |

| MAX3232CDWG4 | DW           | SOIC         | 16   | 40  | 506.98 | 12.7   | 4826   | 6.6    |

| MAX3232IDW   | DW           | SOIC         | 16   | 40  | 506.98 | 12.7   | 4826   | 6.6    |

7.5 x 10.3, 1.27 mm pitch

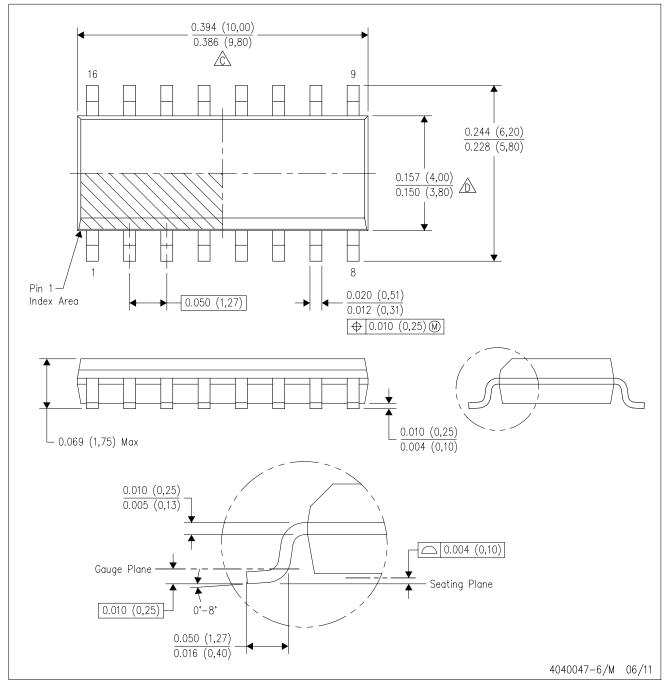

SMALL OUTLINE INTEGRATED CIRCUIT

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

SOIC

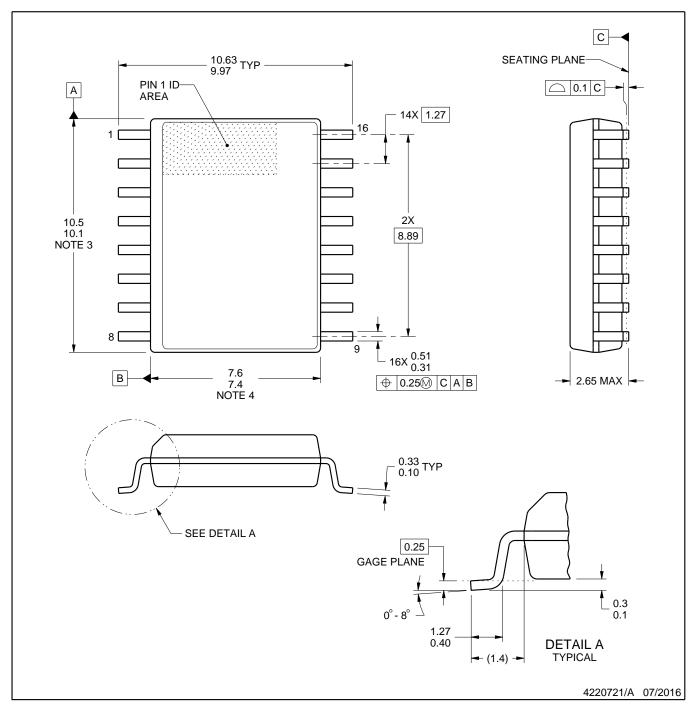

#### NOTES:

- 1. All linear dimensions are in millimeters. Dimensions in parenthesis are for reference only. Dimensioning and tolerancing

- per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm, per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm, per side.

- 5. Reference JEDEC registration MS-013.

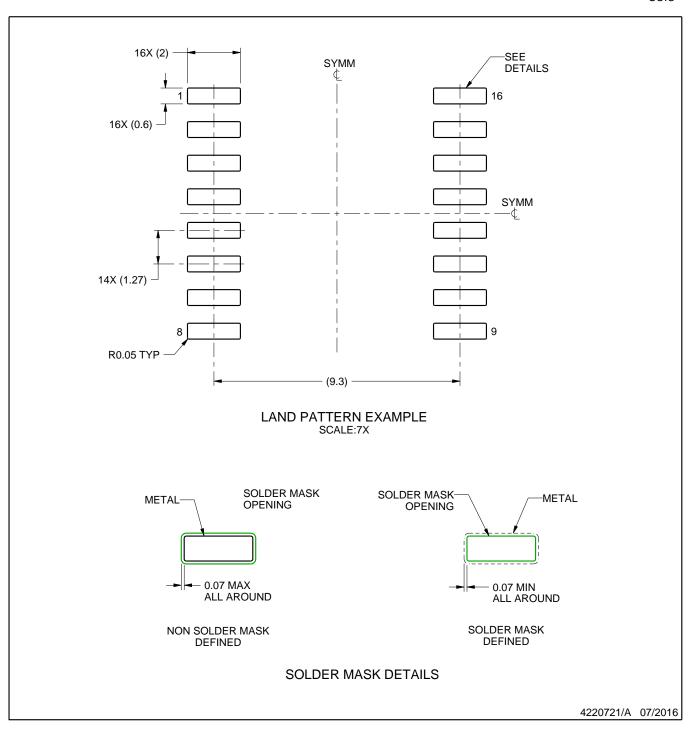

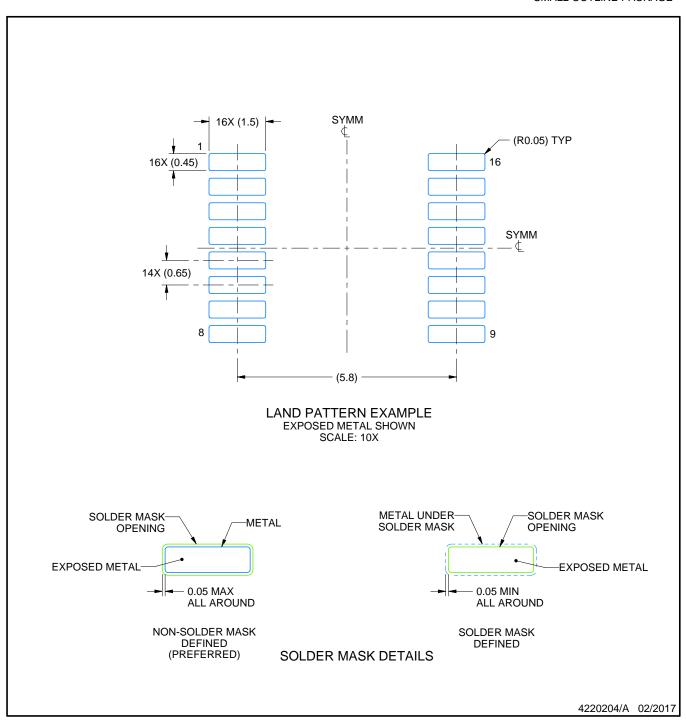

SOIC

#### NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

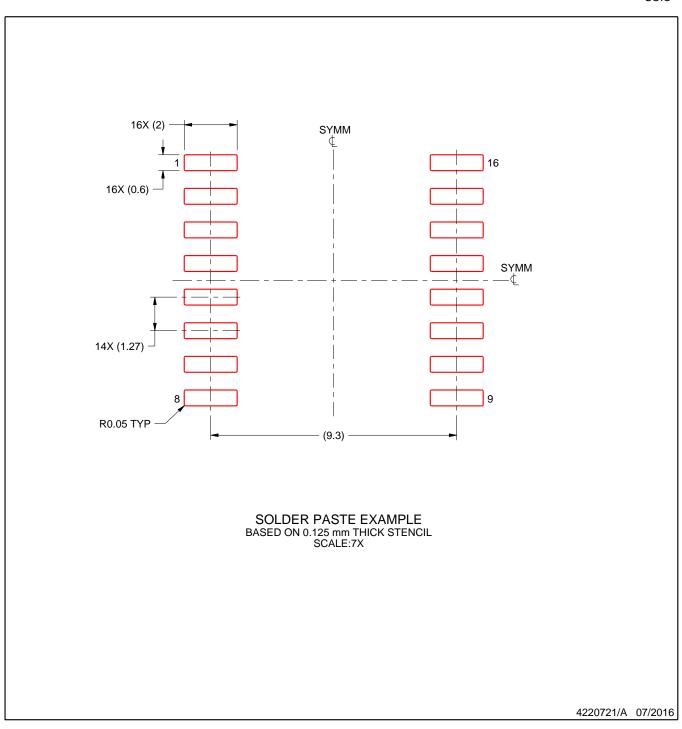

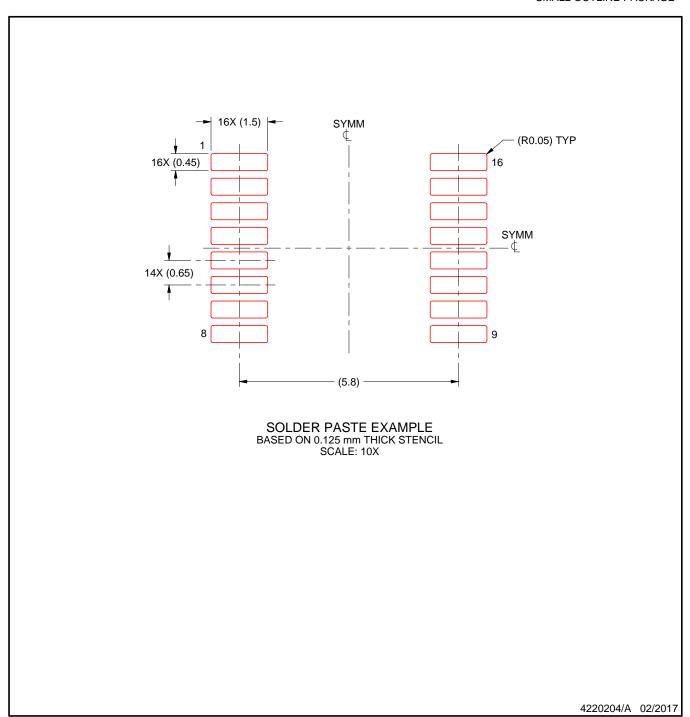

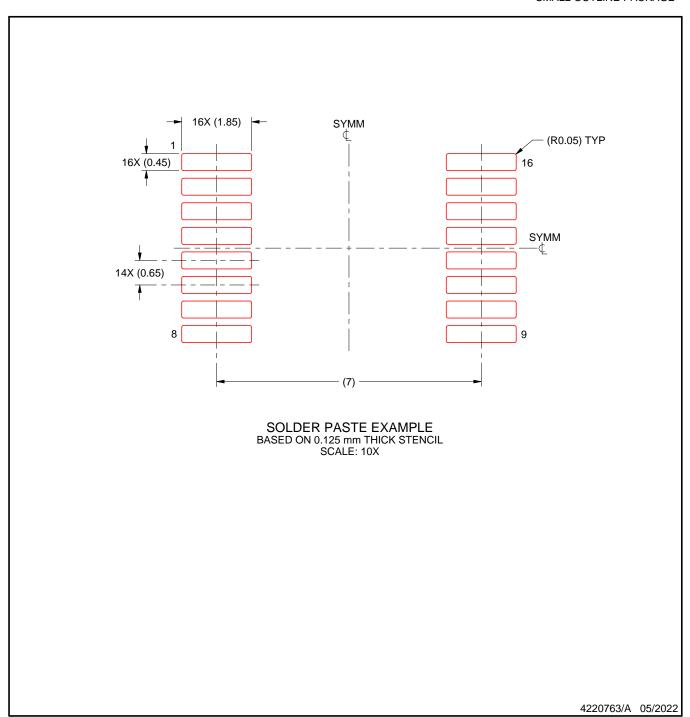

SOIC

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# D (R-PDS0-G16)

## PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AC.

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

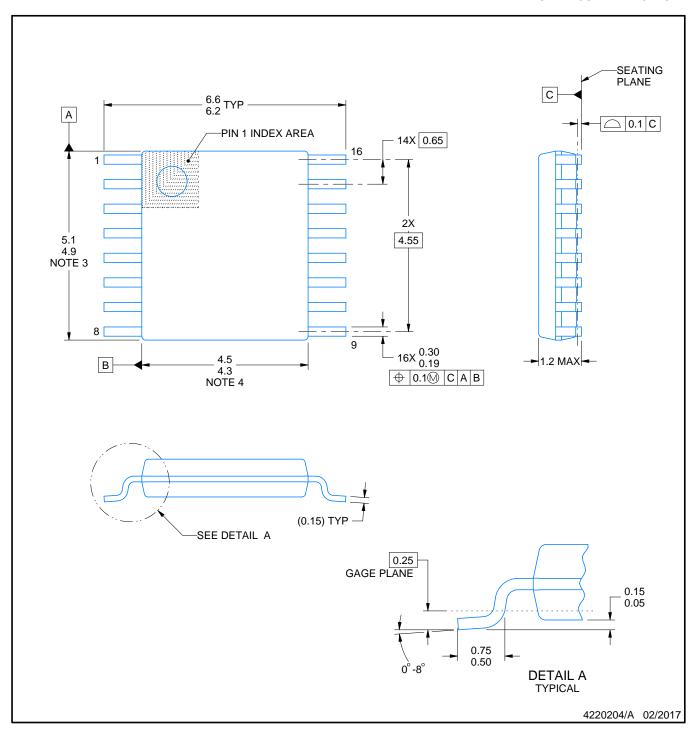

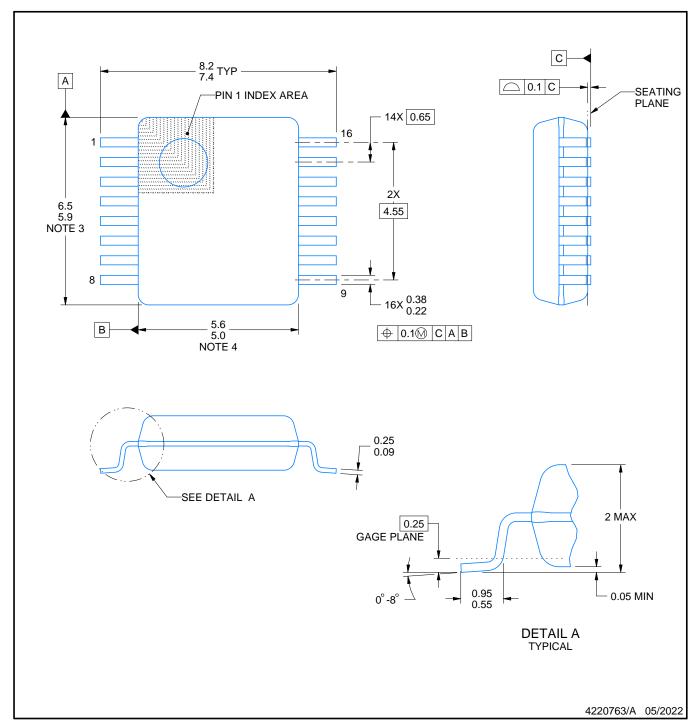

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

4. Reference JEDEC registration MO-150.

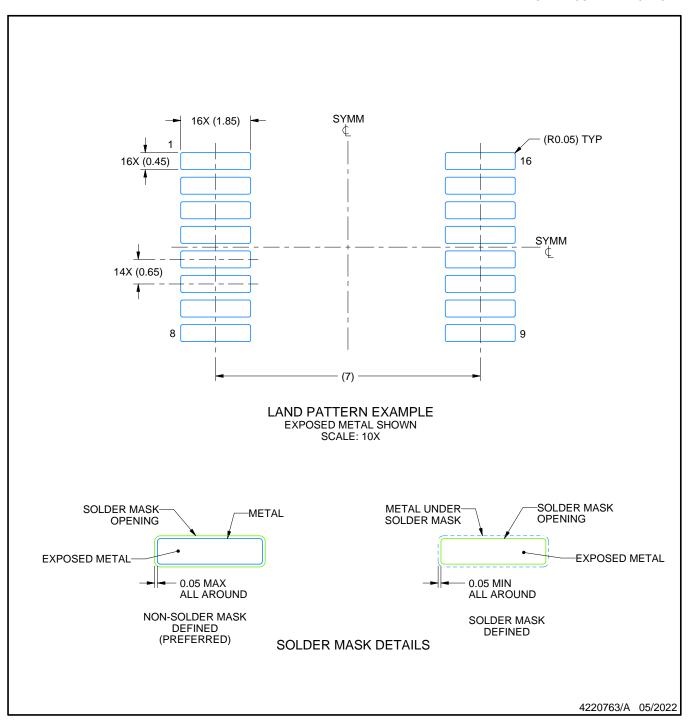

NOTES: (continued)

- 5. Publication IPC-7351 may have alternate designs.

- 6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

NOTES: (continued)

- 7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 8. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス・デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあら ゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、または ti.com やかかる TI 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、TIはそれらに異議を唱え、拒否します。

郵送先住所:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated